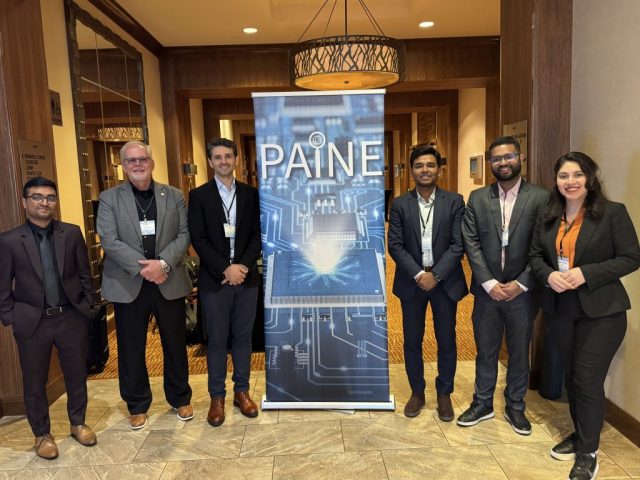

PROGRAM| SPEAKERS| SPONSORSHIP | WINNERS| GALLERY

Past Program Schedule

DAY 1| DAY 2| DAY 3*All Times are in CST

Time

Day 1: October 14, 2025

7:30 – 9:00

Registration & Breakfast

8:45 – 9:00

Opening Remarks – PAINE 2024 Awards

General Chair and Program Chair

Plenary Session I

Chair: Nathan Edwards – Rapid Innovation & Security Experts Inc.

9:00 – 9:30

Keynote Talk I: Bridging Virtual and Physical: Accelerating U.S. Semiconductor Innovation with Digital Twin Technologies

Dr. Paris Stringfellow – SMART USA Institute

9:30 – 10:00

Break

SESSION I: Invited Talks

Chair: Dr Edward Jimenez – Sandia National Laboratory

10:00 – 10:20

Metrology Challenges & Solutions for Hybrid Bonding

Dr. Bongsub Lee – ADEIA

10:20 – 10:40

The Evolution of Electronics Packaging to Chiplet Architecture

Dr. Charles Woychik – Nhanced Semiconductors, Inc.

10:40 – 11:00

Buried Truths: Opportunities in Non-Invasive Thermal Analysis for 2.5D/3D ICs

Dr. Mo Shakouri – Microsanj

11:00 – 11:20

Enhancing Supply Chain Trust & Assurance with AI

Dr. Matthew Areno – Midwest Microelectronics Consortium

11:20 – 11:40

FSE Assurance and 3-D Advanced HI Packaging Failure Analysis Lab

Matt Walsh – Florida Semiconductor ENGINE

11:40 – 1:00

Lunch

Plenary Session II

Chair: David Torres – Red Ballon Security

1:00 – 1:20

Visionary 1: Navigating the Post-Generative AI Era of Failure Analysis

Dr. Joy Liao – Nvidia

SESSION II: Special Session SEMI

Chair: Anshu Bahadur

1:20 – 2:20

Virtual Metrology

Dr. Min Gao – EMD Electronics

Steve Cho – Gauss Labs

Dr. Surya Kalidindi – Multiscale Technologies

2:20 – 2:50

Break

SESSION III: Paper Presentations

Chair: Emily Haines – Battelle

2:50 – 3:10

Lurking in the Shadows: Challenges for X-Ray Inspection to Uncover Electromigration-Based Hardware Trojans in Advanced Packaging

Katayoon Yahyaei – University of Florida

3:10 – 3:30

X-Ray Fault Injection Localization with a Shield on Powered and Unpowered Devices

Paul Grandamme – Université Jean Monnet-France

3:30 – 3:50

Metaheuristic Color Scheme Strategies for Enhanced Visual Inspection of 3D IC Layouts

Zhansen Shi – National University of Singapore

3:50 – 4:10

Magnetic Field Imaging using Diamond Nitrogen-Vacancy Centers for Fault Detection and Security of Semiconductor and Superconductor Electronics

Pauli Kehayias – MIT Lincoln Laboratory

4:10 – 5:30

Exhibit and Poster Session

5:30 – 7:30

Social Event

Time

Day 2: October 15, 2025

7:00 – 8:30

Breakfast

Plenary Session I

Chair: Dr. Adam Waite – Battelle

8:30 – 9:00

Keynote Talk II: Next-Generation Microelectronics Manufacturing

Saverio Fazzari – Booz Allen Hamilton

9:00 – 9:30

Visionary 2: Keeping up with Moore’s Law: Silicon Reliability and Product Qualification challenges due to Technology Scaling

Amit Marathe – Google

9:30 – 9:50

Break

SESSION IV: Fireside Chat

Moderator: Saverio Fazzari

9:50 – 10:50

Topic: The Intersection of Government and Commercial Microelectronics

Dr. William Zortman, Dr. Matthew Areno

10:50 – 11:10

Break

SESSION V: Invited Talks

Chair: Dr. Eric Cotts – Binghamton University

11:10 – 11:30

Hardware security vulnerabilities: Lessons learnt after nearly 800+bugs

Dr. Jeyavijayan “JV” Rajendran – Texas A&M University

11:30 – 11:50

Adventures in Hyperspectral Computed Tomography for Non-destructive Hardware Evaluation

Dr. Eric Goodman – Sandia National Laboratories

11:50 – 12:10

Electron Beam Assisted Back-Contact Free Electrical Atomic Force Microscopy

Dr. Umberto Celano – Arizona State University

12:10 – 12:30

Defect Imaging of Emerging Memory Materials via Electro-Optical Characterization

Dr. Thomas Beechem – Purdue University

12:30 – 2:00

Lunch

SESSION VI: Panel Discussion

Moderators: Saverio Fazzari – Booz Allen Hamilton

2:00 – 3:30

The Role of AI in Redefining Physical Assurance

Dr. Adam Kimura – Battelle

Dr. Sarah Paluskiewicz – Northrop Grumman

Dr. Navid Asadi – University of Florida

Dr. Julian Warchall – IBM Research

Dr. Edward Jimenez – Sandia National Laboratories

3:30 – 4:00

Break

SESSION VII: Paper Presentations

Chair: Daniel Homiak – Lockheed Martin

4:00 – 4:20

Advancing Microelectronics Evidence-Based Assurance while Preserving Confidentiality: Copia

Nikhil Shenoy – Colvin Run Networks, Inc.

Nathan Edwards – Rapid Innovation and Security Experts, Inc.

4:20 – 4:40

Analysis of Temperature Effect on SRAM PUF For Low Cost Applications

Sayan Samanta – The University of Alabama in Huntsville

4:40 – 5:00

A Quantitative Means for Assessing Failure in SnBi-Based Solder Joints During Current Stressing

Eric Cotts – SUNY Binghamton

5:00 – 5:20

Post-Silicon Functional Verification and Validation: Chip to RTL Analysis

Tim McDonley – Battelle Memorial Institute

5:20 – 5:40

Evaluating multimodal foundation models for few-shot PCB identification and reasoning

Zachary Burns – Leidos Innovations Center

Time

Day 3: October 16, 2025

7:00 – 8:00

Breakfast

Plenary Session I

Chair: Dave Via – Midwest Microelectronics Consortium

8:00 – 8:30

Keynote Talk III: Secure Design-for-Test and Inspection Techniques for Trusted 3DIC

Antonio De la Serna – Siemens EDA

8:30 – 8:50

Hardware-Enabled Mechanisms for Verifying Responsible AI Development

Will Hodgkins – Center for AI Safety

8:50 – 9:30

Break

SESSION VIII: Invited Talks

Chair: Nikhil Shenoy – Colvin Run Networks

9:30 – 9:50

Mathematical Approaches to Microelectronics Assurance

Dr. Whitney Batchelor – Graf Research

9:50 – 10:10

Deep-Learning Side-Channel Analysis

Dr. Boyang Wang – University of Cincinnati

10:10 – 10:30

Chiplets and Reliability

Dr. Jason Rupe – Cablelabs

10:30 – 10:50

Break

SESSION IX: Paper Presentations

Chair: Dr. Sneha Sudhakaran – Florida Institute of Technology

10:50 – 11:10

Exploiting Electron-Beam Probing for Information Leakage in Advanced-Node Integrated Circuits

M Shafkat M Khan – Thermo Fisher Scientific Inc.

11:10 – 11:30

Efficient Side-channel Leakage Assessment Using Deep Learning-based Feature Extractor and ANOVA

Yuta Fukuda – National Institute of Advanced Industrial Science and Technology – Japan

11:30 – 11:50

Enabling Algorithm Detection in the Presence of Interrupts: Using HAL for Side-Channel Interrupt Detection and Mitigation

Kevin Pintong – Binghamton University

11:50 – 1:00

Lunch

SESSION X: Paper Presentations

Chair: Dr. Akshay Kulkarni – Prairie View A&M University

1:00 – 1:20

Analyzing Sources of Fingerprints in Wireless Modules Using Microwave Measurements

Vishnuvardhan Iyer – National Institute of Standards and Technology

1:20 – 1:40

Multi-Granular Information Flow Tracking in RISC-V based SoCs

Dhruvakumar Aklekar – University of North Carolina at Charlotte

1:40 – 2:00

AuthenTree: A Scalable MPC-Based Distributed Trust Architecture for Chiplet-based Heterogeneous Systems

Ishraq Tashdid – University of Central Florida

2:00 – 2:20

FirmEM: Firmware Flashing Detection via Unintentional Electromagnetic Emissions

Elvan Ugurlu – Aether Argus Inc.

2:20 – 2:50

Break

SESSION XI: Paper Presentations

Chair: Dr. Rayhane Ghane – Ficontec

2:50 – 3:10

A Defense Electronics Supply Chain Root Cause Analysis-based Model to identify data features that are viable for counterfeit predictive analytics

Konstantinos Belesis – George Washington University

3:10 – 3:30

Integrated-Circuit Supply Chain Verification Using Mask Set Comparison in the Open Source Context

Olivier Thomas – Texplained – France

3:30 – 3:50

Power Spectrum Analysis-Based Counterfeit Screening: A Hardware Comparison

Devon Richman – University of Maryland

3:50 – 4:00

Closing

General Chair and Program Chair

Speakers

Dr. Rob Aitken

Program Manager | CHIPS R&D Office

Dr. Tim Morgan

Technical Director | Microelectronics Commons

Matt Walsh

Chief Engineer | Florida Semiconductor ENGINE

Dr. Bongsub Lee

Sr. Director, Materials and Metrology Engineering | ADEIA

Will Hodgkins

Program Director | Center for AI Safety

Dr. Umberto Celano

Associate Professor | Arizona State University

Dr. Julian Warchall

Technology Business Development Executive | IBM Research

Dr. Thomas Beechem

Associate Professor | Purdue University

Saverio Fazzari

Senior Lead Engineer | Booz Allen Hamilton

Dr. Sarah Paluskiewicz

Sr. Principal AI Engineer | Northrop Grumman

Samuel Wood

Global Manufacturing & Digitalization Exec | EMD Electronics

Dr. Anis Rahman

Chief Technology Officer and CEO | Applied Research & Photonics, Inc.

Dr. Matthew Areno

Co-Chair of Secure Edge | Midwest Microelectronics Consortium

Dr. Jim Booth

Guided Wave EM Group Leader | NIST

Dr. Jason Rupe

Distinguished Technologist | Cablelabs

Dr. Paris Stringfellow

Deputy Chief Digital Officer | SMART USA Institute

Amit Marathe

Head of Phone Technology Reliability Engineering | Google

Dr. Joy Liao

Sr. Manager Silicon Failure Analysis | Nvidia

Dr. June Lau

Physicist and Data Specialist | NIST

Dr. Mo Shakouri

Founder & CEO | Microsanj

Dr. Adam Kimura

R&D Technical Director | Battelle

Dr. Charles Woychik

VP of Sales & Marketing | NHanced Semiconductors, Inc.

Antonio de la Serna

Principal Director of Strategic Technology | Siemens EDA

Dr. Whitney Batchelor

Director of Research | Graf Research

Dr. Eric Goodman

Principal Member Technical Staff | Sandia National Laboratories

Dr. Boyang Wang

Program Chair in Cybersecurity Engineering | University of Cincinnati

Dr. Surya Kalidindi

CEO & Co-Founder | Multiscale Technologies

Dr. Nelson Hastings

Cybersecurity and Privacy Applications Group | NIST

Dr. Guru Venkataramani

Security Components and Mechanisms Group | NIST Professor | George Washington University

Dr. Edward Jimenez

Distinguished Optical Scientist and Engineer | Sandia National Laboratories

PAINE 2025 Winners

Best Paper

Metaheuristic Color Scheme Strategies for Enhanced Visual Inspection of 3D IC Layouts

Jie Zhang, Zhansen Shi, Hanchen Wang, Zhuoyang Zhang, Lucas Lum, Quanhao Gan, Shaoyu Cai, Eng Tat Khoo, Yeow Kheng Lim | National University of Singapore

Best Lab Demo

Reliable and Assured Microelectronics Lab (RAMLAB)

Director: Dr. Biswajit Ray | Colorado State University

Video LinkBest Poster

Towards Improving Side-Channel Analysis in FPGAs using the Hardware Response

Meghana Jain and Douglas Summerville | Binghamton University

Gallery